基于EASY CORE芯片组的专用PLC设计

|

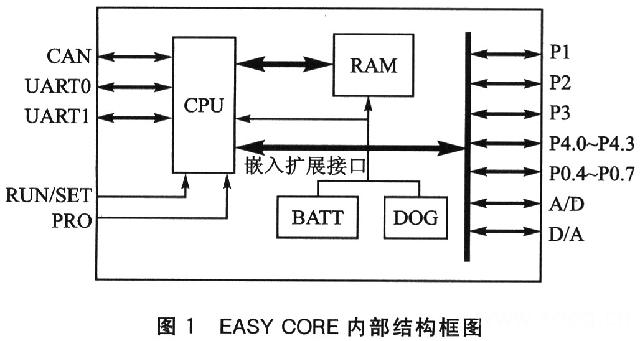

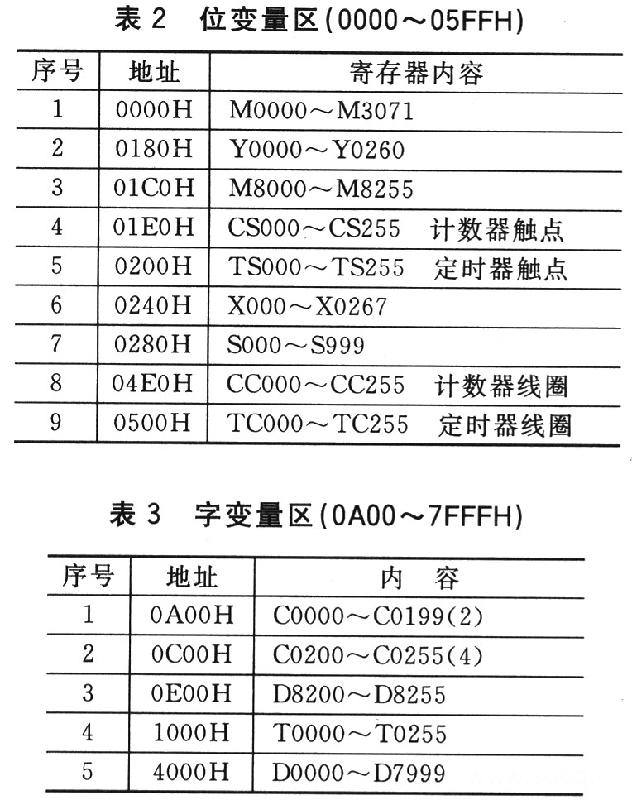

1 EASY CORE的PLC芯片组 EASY CORE是一个加载了EASY嵌入式PLC软件平台的核心芯片组,用于设计PLC,其内部结构框图如图1所示。  1.1 EASY CORE内核 内核采用C8051F040混合式高性能单片机,片内有64个I/O端口引脚、1个CAN2.0B集成控制器、12位的ADC、PGA和模拟复用开关、2个12位DAC、64 KB的可编程Flash存储器、4 352(4 096+256)字节的RAM、SPI、SMBus/I2C、2个UART串行接口、5个16位通用定时器,可编程计数/定时阵列有6个捕捉/比较模块,片内有看门狗定时器、VDD监视器、温度传感器等,工业温度范围-45℃~+85℃内采用2.7~3.6 V的工作电压。 可通过设置开关交叉控制寄存器,将片内的计数器/定时器、串行总线、硬件中断、ADC转换启动输入、比较器输出以及微控制器内部的其他数字信号配置为在I/O引脚输出。允许用户根据自己特定的应用选择通用端口I/O和所需数字资源的组合。 内核采用实时操作系统,加载了与FX2N PLC兼容的梯形图语言的监控程序,指令系统与通信格式与FX2NPLC兼容。因而可以采用FX2N PLC软件编程,也可采用通用组态软件监控。 1.2 用户驱动开发接口 用户根据接口规范,可以嵌入完成特定功能的汇编程序,实现I/O点配置、AD/DA以及其他特殊的功能。 ①嵌入程序代码存放地址为E000H~F7FFH。  ③位寄存器区中用户使用区(20H~23H)。 ④直接寻址寄存器中用户使用区(58H~67H)。 ⑤外部RAM中用户使用区(3600H~3FFFH)。 ⑥PLC资源区(0000~5080H),系统程序和用户程序均可访问。位变量区和字变量区分别如表2、表3所列。

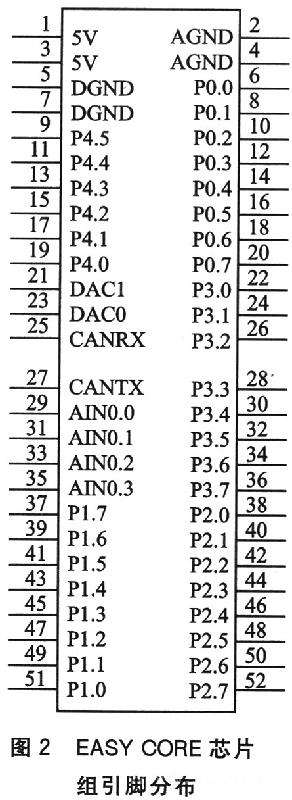

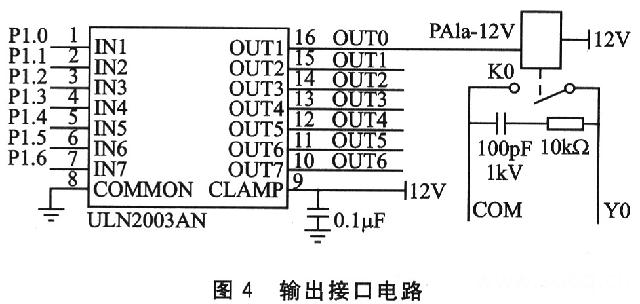

2 应用实例 现以8个输入点、7个输出点PLC设计为例,说明专用PLC的设计过程。 2.1 硬件电路设计 硬件电路由芯片组、电源电路、输入接口电路、输出接口电路、通信接口电路等组成。 2.1.1 EASY CORE芯片组外围引脚 EASY CORE芯片组引脚分布如图2所示。  (1)特殊用途引脚 2.1.2输入/输出接口电路 输入接口电路:输入点为X0~X7(图中只画一条),输入接口采用光电隔离器TLP180,防止外界干扰,接口电路如图3所示。P3.0为高电平电压3.3 V。  输出接口电路:输出点为Y0~Y7(图中只画一条),输出信号经2003驱动输出继电器或晶体管,如图4所示。ULN2003AN为7路驱动器。

PLC指令的解释、与上位机的通信等核心功能已由EASY CORE内核完成;用户程序只要根据接口规范,结合用户设计要求,编制少量的接口程序。 用户程序主要是把外部接口电路与内核软件的输入、输出缓冲区相联系。读P3.0~P3.7(X0~X7),送到相应RAM-PX,把RAM—PY(Y0~Y6)数据输出到P1.0~P1.6(Y0~Y6)。主要程序结构如图5所示。  (主要程序略——编者注) 3 结 论 基于芯片组的嵌入式PLC,能有效弥补通用PLC在低端市场的不足,与工艺对象结合紧密。只要解决好电路的抗干扰设计问题,嵌入式PLC有较大的市场前景。目前,笔者已将成功应用于龙门铣床的改造。 |

声明:本网站所收集的部分公开资料来源于互联网,转载的目的在于传递更多信息及用于网络分享,并不代表本站赞同其观点和对其真实性负责,也不构成任何其他建议。本站部分作品是由网友自主投稿和发布、编辑整理上传,对此类作品本站仅提供交流平台,不为其版权负责。如果您发现网站上所用视频、图片、文字如涉及作品版权问题,请第一时间告知,我们将根据您提供的证明材料确认版权并按国家标准支付稿酬或立即删除内容,以保证您的权益!联系电话:010-58612588 或 Email:editor@mmsonline.com.cn。

- 暂无反馈